# 適用於次臨界區操作之對稱式 NAND 閘

葉威志

林進發 朝陽科技大學 -助理教授 e-mail: jflin @cyut.edu.tw 林文昌 朝陽科技大學 -大學部 e-mail: s10030059

朝陽科技大學 -大學部 e-mail: s10030052 洪紳寶 朝陽科技大學 -大學部 e-mail: s10030036

李育晟 朝陽科技大學 -研究所 e-mail: s10230613 @cyut.edu.tw

@cyut.edu.tw

@cyut.edu.tw

@cyut.edu.tw

# 摘要

對稱式及閘(symmetric NAND gate)由於成功解決了基體效應的問題(body-effect),具有較高的切換速度因而廣泛的應用在高速IC的應用場合。在本論文中,我們將此電路與傳統及閘操作在次臨界區間進行分析與比較,經由佈局後模擬(post-layout simulation)其結果顯示,對稱式及閘不僅可以提供較高的切換速度與功率延遲乘積比(power-delay-product),同時解決上述之基體效應的影響,而有更低的操作電壓。當運行在1KHz時,與傳統及閘相比對稱式及閘分別可以節省40%和10.5%的最大與平均功率延遲乘積比。

關鍵詞:對稱式、超低電壓、次臨界電壓。

# 1. 前言

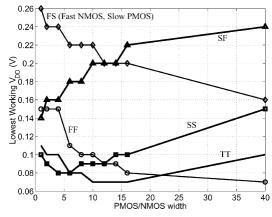

目前已提出許多低功耗晶片設計,主要是

讓電路操作在次臨界操作區間大幅抑制其功率消耗。而所謂的臨界操作區是指是當操作電壓  $V_{T}$  ,即閘極電壓  $V_{S}$  尚未達到臨界電壓  $V_{T}$  ,Id值應該要等於零,然而實際上,即使  $V_{S}$  未到達  $V_{T}$  ,仍然會存在一微量的  $I_{S}$  的  $I_{S}$  以此時的  $I_{S}$  因無不電流,不 實際上,即使  $I_{S}$  以為次臨界電流,藉助此一 微弱電流進行動作。一般而言,當操作在次臨界區時,由於電晶體並沒有完全導通,因此操作速度將非常的緩慢,特別是  $I_{S}$  pMOS 所帶來的負面問題。另一個需面對的問題則是製程偏移的影響,如  $I_{S}$  的最低工作電壓的影響。由此圖可以得知,傳統的  $I_{S}$  的影響。由此圖可以得知,傳統的  $I_{S}$  的影響。由此圖可以得知,傳統的  $I_{S}$  以  $I_{S}$  的  $I_{S}$  以  $I_{S}$  的  $I_{S}$  以  $I_{S}$  以  $I_{S}$  的  $I_{S}$  以  $I_{S}$  以  $I_{S}$  以  $I_{S}$  以  $I_{S}$  的  $I_{S}$  以  $I_{S}$  以

在本論文中,我們將已成功應用在高速場合的對稱式及閘(symmetric NAND gate)將其操作在臨界區間進行模擬。經過後模擬我們發現,此一電路由於改善基體效應(body-effect)不僅可獲得較高的切換速度,同時亦可操作在更低操作電壓,換言之,對稱式電路結構將比傳統電路更適用於次臨界區間的操作式。

Fig.1 可操作最低電壓時的pMOS/nMOS比例

(TSMC-0.18um).

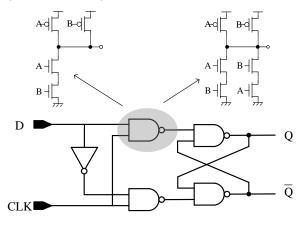

Fig.2 傳統及閘與對稱式及閘

# 2. 對稱式電路

如 Fig.2 所示,左上方為傳統及閘(NAND gate)右上方則為對稱式及閘(symmetric NAND gate),兩個電路的最大不同點在於後者增加額外的一組 nMOS 電路加快其放電速度。 此一特點使該電路已經成功的應用在各類的高速晶片設計[3]。其電路的動作原理如下:我們考慮 此電路的 最差 傳遞 情況 即輸入信號 AB=11,同時 A 信號比 B 信號早先進入電路。因為,位於下方的 nMOS(B 信號控制)還未導

通的情況下,造成上方的 nMOS 產生基體效應 (body-effect),此一效應會將 MOS 元件的臨界電壓(V<sub>TH</sub>)拉高使其傳導效率降低。當同一情況發生在對稱式電路時,由於第二組放電路徑的信號接續方式刻意與第一組放電路徑相反,換言之上述的基體效應將不會發生, 再加上兩個路徑的同時放電,因此對稱式電路有非常良好的切換速度[3]。

經由上述的分析我們可以得知,對稱式電路除了可以提升切換速度外,同時亦可抑制基體效應的發生,當 MOS 操作在次臨界區時(及 VDD VTH 的場合),由於 VTH 電壓未被提高,因此該電路應當會有更好的性能表現。為了探討與證明此一現象,我們將傳統及閘與對稱式及閘分別組成一個全及閘設計的靜態栓鎖電路(fully NAND-based static latch)如 Fig.2 所示。挑選此一電路之原因,在於序向邏輯電路在現今IC 晶片中幾乎占了 30-50%的面積與功耗[2]。最後,藉由完整的後模擬(post-layout simulation)進行分析與驗證,其完整的結果我們將在下一個章節呈獻。

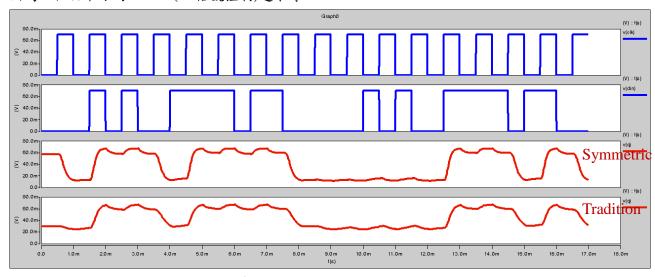

Fig.3 後模擬之波形圖@70mV/1Khz

表 1. 栓鎖電路性能比較表@0.1V/1KHz

|                            | Tradition-NAND Based | Symmetric NAND-Based |

|----------------------------|----------------------|----------------------|

| Total Transistor-Count     | 18                   | 26                   |

| Layout Area (um²)          | 138.5                | 173.07               |

| Minimum Supply Voltage     | 70mV                 | 60mV                 |

| Operation Speed (uS)       | 218                  | 140                  |

| Power-delay-product (e-16) | 6.34                 | 3.79                 |

#### 3. 模擬結果

在本論文中,我們採用由台積電所提供之TSMC 1P6M 0.18um COMS 製程將上述電路進行實現與模擬,藉由 Fig.1 的製程變異結果在pMOS/nMOS 的比例上我們挑選適用於次臨界區間操作的 6:1 即 pMOS 為 3.0u 而 nMOS 為 0.5u。操作電壓部分,TSMC 0.18um CMOS 製程的臨界電壓-V<sub>TH</sub> 約為 0.45V,因此我們挑選 300mV 至最低的 60mV,操作頻率則固定在 1Khz,同時在輸出接上一個同樣尺寸大小的反相器當作負載用以量測相關的性能數據。

Fig.3 為兩個電路的後模擬波形圖,其中上方為兩個輸入信號 CLK 與 Data-IN,接續兩個波形分別是對稱式電路組成的栓鎖電路與傳統及閘所組成的電路輸出波形 Q。由此圖可以得知,對稱式電路因為有兩個放電路徑的幫助,因此最低擺幅電壓可以壓低至 10mV,而傳統電路則僅能到 30mV 已接近無法正確操作的臨界點。表一為此兩個電路的性能比較列表,由此比較可以得知,對稱式設計在增加 20%的電路面積情況下,改善了電路所有的性能。其中速度增快 150%,最小操作電壓降低 20%,功率延遲乘積比亦節省 40%。

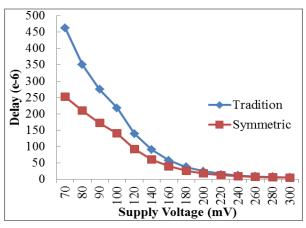

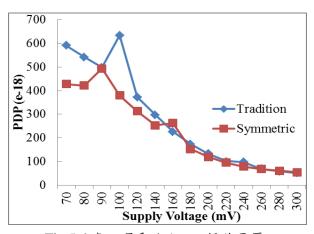

我們進一步模擬這兩個電路對於操作電壓 改變得影響,分別記錄在 Fig.4 與 Fig.5。在操 作電壓部分,由於傳統電路所組成的栓鎖電路 無法操作在 60mV,因此最低數據只記錄到 70mV。Fig.4 可以發現對稱式電路展現其電路 上的最大優點,在速度上獲得全面的領先,當 操作電壓為 70mV 時,可大幅提升 1.8 倍的操作速度。此一結果亦反應在功率延遲乘積比如 Fig.5 所示。Fig.5 的結果也顯示,對稱式電路 的電路轉態點會比傳統電路提早約 10mV 出現,此一現象指出它將更適用於操低電壓應用的場合。最後,我們計算在此操作區間 (70-300mV)的功率延遲乘積比可節省 10.5%。

Fig.4 速度 vs 操作電壓

Fig.5功率延遲乘積比 vs 操作電壓

#### 4. 結論

在本論文中,我們將廣泛應用在高速場合的對稱式及閘將其操作再次臨界區進行分析。經過完整模擬後發現,此一電路由於改善基體效應所帶來的影響,不僅提供更佳的切換速度與功率延遲乘積比,它同時還可以操作在更低操作電壓,可近一步降低電路的功率與能量的消耗。

#### 誌謝

感謝台灣國家晶片系統設計中心(National Chip Implementation Center, CIC) 對於晶片製程與模擬環境的提供與支援。本論文經費來源由國科會計畫NSC 102-2221-E-324-043-所提供。

# 參考文獻

- [1] V. Moalemi, A. Afzali-Kusha, "Subthreshold 1-bit full adder cells in sub-100 nm technologies," *IEEE Computer Society Annual Symposium on VLSI*, pp. 514–515, Mar 2007.

- [2]N.Weste and K.Eshraghian, Principles of CMOS VLSI Design,A System Perspective. Reading,MA:Addison-Wesley,1993.

- [3] Sunghwa Ok; Kyunghoon Chung; Jabeom Koo; Chulwoo Kim; , "An antiharmonic, programmable, DLL-based frequency multiplier for dynamic frequency scaling," *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, vol.18, no.7, pp.1130-1134, July 2010.

- [4] A. Wang and A. Chandrakasan, —A 180 mV FFT processor using subthreshold circuit techniques," in *IEEE Int. Solid-State Circuits Conf. (ISSCC)* Dig. Tech. Papers, 2004, pp. 292–293.

- [5] A. Tajalli, E. J. Brauer, Y. Leblebici, and E. Vittoz, "Subthreshold sourcecoupled

logic circuits for ultra-low power applications," *IEEE J. Solid-State Circuits*, vol. 43, no. 7, pp. 1699-1710. Jul. 2008.

[6] M. Alioto, "Understanding DC behavior of subthreshold CMOS logic through closed-form analysis," *IEEE Trans. Circuits Syst.* I, Reg. Papers, vol. 57, no. 7, pp. 1597–1607, Jul. 2010.